UVM questions

Important UVM Questions

Image Posted on Updated on

- What is uvm_transaction, uvm_object, uvm_component?

The uvm_transaction class is the root base class for UVM transactions. Inheriting all the methods of uvm_object, uvm_transaction adds a timing and recording interface.This class provides timestamp properties, notification events, and transaction recording support.Use of this class as a base for user-defined transactions is deprecated. Its subtype, uvm_sequence_item, shall be used as the base class for all user-defined transaction types.

The uvm_object class is the base class for all UVM data and hierarchical classes. Its primary role is to define a set of methods for such common operations as create, copy, compare, print, and record.

The uvm_component class is the root base class for UVM components. In addition to the features inherited from uvm_object, it has phasing, reporting, hierarchy, configuration, transaction recording and factory.

- Can we have user defined phase in UVM?

Yes, check this link https://www.vmmcentral.org/uvm_vmm_ik/files4/test-phasing-txt.html#User-Defined_Phases

- What is the difference between new() and create?

Create() is a factory method which construct an object. To override an object you need to construct it using create(). if you use set_type_override then before run, factory replaces constructed object with derived object( specified in override). if you use new() then you cant override

- What is analysis port?

The analysis port is used to perform non-blocking broadcasts of transactions. It is by components like monitors/drivers to publish transactions to its subscribers, which are typically scoreboards and response/coverage collectors. For each port, more than one component can be connected. Even if a component is not connected to the port, simulation can continue, unlike put/get ports where simulation is not continued.

- What is TLM FIFO?

This class provides storage of transactions between two independently running processes. Transactions are put into the FIFO via the put_export. transactions are fetched from the FIFO in the order they arrived via the get_peek_export.

- How sequence starts?

A sequence is a series of transaction. User can define the complex stimulus. sequences can be reused, extended, randomized, and combined sequentially and hierarchically in various ways.

First when the body() method is called

1) A transaction is created using “create()” method. If a transaction is created using “create()” method, then it can be overridden if required using uvm factory.2) After a transaction is created, wait_for_grant() method is called. This method is blocking method.

3) In the run task of the driver, when “seq_item_port.get_next_item()” is called, then the sequencer un blocks wait_for_grant() method. If more than one sequence is getting executed by sequencer, then based on arbitration rules, un blocks the wait_for_grant() method.

4) After the wait_for_grant() un blocks, then transaction can be randomized, or its properties can be filled directly. Then using the send_request() method, send the transaction to the driver.

5) After calling the send_request() method, “wait_for_item_done()” method is called. This is a blocking method and execution gets blocks at this method call.

6) The transaction which is sent from sequence , in the driver this transaction is available as “seq_item_port.get_next_item(req)” method argument. Then driver can drive this transaction to bus or lower level.

7) Once the driver operations are completed, then by calling “seq_item_port.put(rsp)”, wait_for_item_done() method of sequence gest unblocked. Using get_responce(res), the response transaction from driver is taken by sequence and processes it.

- What is the advantage of `uvm_component_utils() and `uvm_object_utils() ?

These are ready-made macros to register uvm-component/uvm_object to factory

- What is objection?

Objections provide a facility for coordinating status information between two or more participating components, objects, and even module-based IP.

- What are the benefits of using UVM?

* Standardized verification methodology so no more confusion to choose a methodology to start a project.

* No tool dependency. No more porting issues from one tool to other

* Less confusion for the engineers. Easy to learn and maintain the skill set

* Provides the flexibility and ways to connect the legacy VMM/OVM components

* Backward compatible with OVM and provides the scripts to change OVM environment to UVM. - What is the difference between Active mode and Passive mode?

If the agent is active, subtypes should contain all three sub-components. If the agent is passive, subtypes should contain only the monitor

- What is the difference between copy and clone?

clone() is virtual; copy() is non-virtual. And clone() is a method of the original object; copy() is a method of the target object.

That means clone() creates a copy an object of the same class type as the original. With copy(), the original object could be a subclass of the target object’s type with additional class properties that will not get copied. Just a note, in UVM, copy calls the virtual do_copy() - What is factory?

1) Registration (`uvm_*utils)

2) Construction (static function T create(string name, uvm_component parent, string context = ” “)

3) Overriding (set_*_override)

The factory method design pattern defining a separate method for creating the objects. , whose subclasses can then override to specify the derived type of object that will be created.Using this method, objects are constructed dynamically based on the specification type of the object. User can alter the behavior of the pre-build code without modifying the code. From the testcase, user from environment or testcase can replace any object which is at any hierarchy level with the user defined object.

- What are the types of sequencer? Explain each?

In pull mode , uvm_sequencer is connected to uvm_driver , in push mode uvm_push_sequencer is connectd to uvm_push_driver

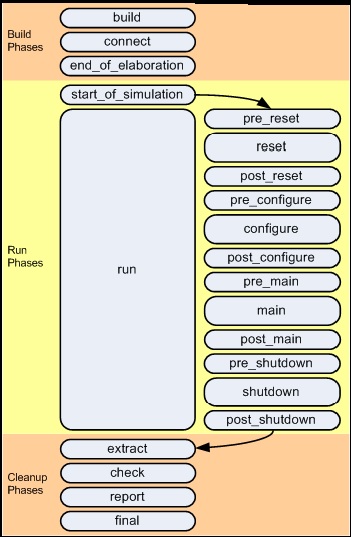

- What are the different phases of uvm_component? Explain each?

- How set_config_* works?

Configuration is a mechanism in UVM that higher level components in a hierarchy can configure the lower level components variables. Using set_config_* methods, user can configure integer, string and objects of lower level components.

- What is super keyword? What is the need of calling super.build() and super.connect()?

– Super keyword is to call the parent class method.

– Super.build() is top-down method, it is important for instantiating the verif-components.

– Super.connect() is bottom-up method, it is important for connecting the tlm ports, tlm sockets and setting explicit phase timeouts. - What is the different between set_config_* and uvm_config_db ?

- What are the different override types?

Type & Instance Overrides set_inst_override_by_type set_inst_override_by_name Configures the factory to create an object of the override’s type whenever a request is made to create an object of the original type using a context that matches full_inst_path. set_type_override_by_type set_type_override_by_name Configures the factory to create an object of the override’s type whenever a request is made to create an object of the original type, provided no instance override applies. - What is virtual sequence and virtual sequencer?

Virtual sequencer is also derived from uvm_sequencer like any other non-virtual sequencer but is not attached to any driver. Virtual sequencer has references to the sequencers we are trying to control. These references are assigned from top environment to the non-virtual sequencers.

Virtual sequences are same as any other sequence but it is associated to a virtual sequencer unlike non-virtual sequences, hence it needs to indicate which non- virtual sequencer it has to use to execute the underlying sequence. Also note that virtual sequence can only execute sequences or other virtual sequences but not the items. Use `uvm_do_on/`uvm_do_on_with to execute non-virtual sequences and `uvm_do/`uvm_do_with to execute other virtual sequence - Explain end of simulation in UVM?

In UVM end of simulation is based upon the objections, if all of the objections raised are dropped then that phase is complete and next phase starts. Once all of run-phases are completed that means, end of simulation and test enters into cleanup-phases (i.e Extract, Check, Report)

- How to declare multiple imports?

using uvm *imp_decl macro, see example`uvm_analysis_imp_decl(A_side).

`uvm_analysis_imp_decl(B_side).

`uvm_put_port_imp_decl(X_side)

`uvm_put_port_imp_decl(Y_side) - What is symbolic representation of port, export and analysis port?

- What is the difference in usage of $finish and global stop request in UVM?

- What is the difference between `uvm_do and `uvm_rand_send?

`uvm_create -> sequencer.wait_for_grant() -> pre_do(1) -> item.randomize() ->mid_do() ->sequencer.send_request() -> sequencer.wait_for_item_done() ->post_do(),`uvm_send:: This macro processes the item or sequence that has been created using `uvm_create. The processing is done without randomization. Essentially, an `uvm_do without the create or randomization.

- Why we need to register class with uvm factory?

So that the advantages of factory pattern (overriding by instance/name) can be used.

- diff between uvm_transaction and uvm_seq_item?

The uvm_sequence_item contains additional variables to allow the object to be utilized on a sequencer/driver. Since the additional overhead is minimal and the goal is to have transactions created during sequences, you should always use uvm_sequence_item and not uvm_transaction.

- can we use set_config and get_config in sequence ?

- What is uvm_heartbeat ?

- UVM TLM 1.1

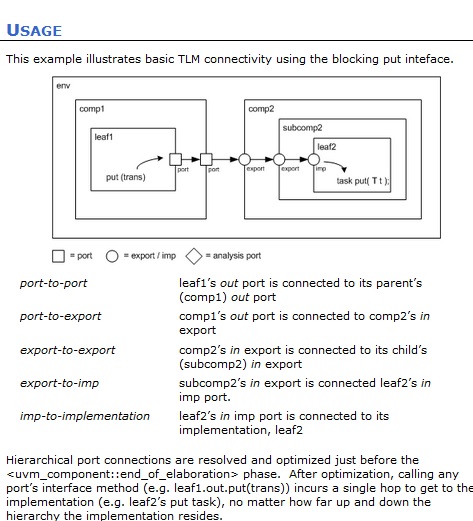

Ports define which access methods to use. There are twenty-three port classes in TLM 1. Each port is a subclass of the

uvm_port_baseclass, which in turn is a subclass of theuvm_tlm_if_baseclass (or a subclass of theuvm_sqr_if_baseclass in case of theuvm_seq_item_pull_portExports are used when you promote imps to a parent component. Similar to the ports, each export is a subclass of theuvm_port_baseclass, which in turn is a subclass of theuvm_tlm_if_baseclass (or a subclass of theuvm_sqr_if_baseclass in case of theuvm_seq_item_pull_export)Imps provide the implementation of access methods. To be precise, the imps delegate the implementation to the component that actually implements the access methods. The type of the component is passed as a parameter when an imp is instantiated. Similar to the ports and exports, each imp is a subclass of the

uvm_port_baseclass, which in turn is a subclass ofuvm_tlm_if_baseclass (or a subclass of theuvm_sqr_if_baseclass in case of theuvm_seq_item_pull_imp** Check link **

http://cluelogic.com/2014/04/uvm-tutorial-for-candy-lovers-tlm1/